#### Isolated or Non-isolated configuration LED driver with active PFC

January 2013

#### **General Description**

The IS31LT3916 is a primary side, peak current mode, isolated or non-isolated type HBLED driver. The device works at a constant frequency in discontinuous conduction mode to provide a constant power to the output. It eliminates the need for an opto-coupler, TL431, or any other type of secondary side feedback. It operates from a wide input voltage range of 85VAC to 265VAC.

The IS31LT3916 integrates over current protection, over voltage protection, as well as includes a thermal shutdown to halt the switching action in the case of abnormally high operating temperatures.

#### Features

- Power factor correction to > 0.95

- 5% typical current accuracy

- High efficiency

- No loop compensation required

- Wide input voltage range: 85V to 265VAC

- Isolation and Non-isolation application

- Internal over-temperature protection

- Over voltage protection

- Primary side over current protection

#### **Applications**

- LED bulb lamp

- LED tube lamp

- General LED Lighting

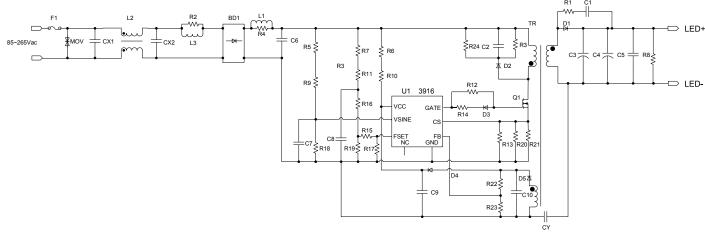

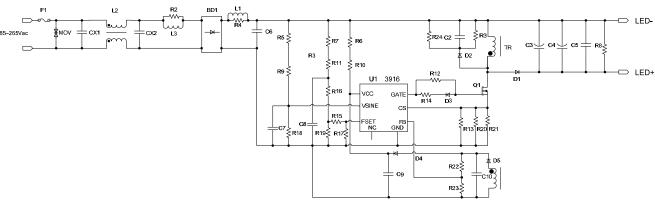

#### **Typical Operating Circuit**

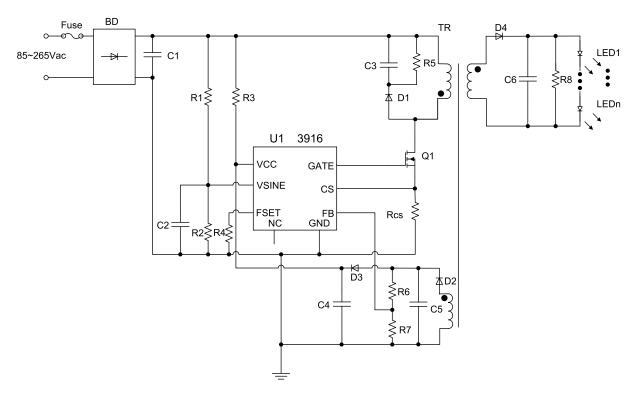

Figure 1 Typical Operating Isolated Circuit

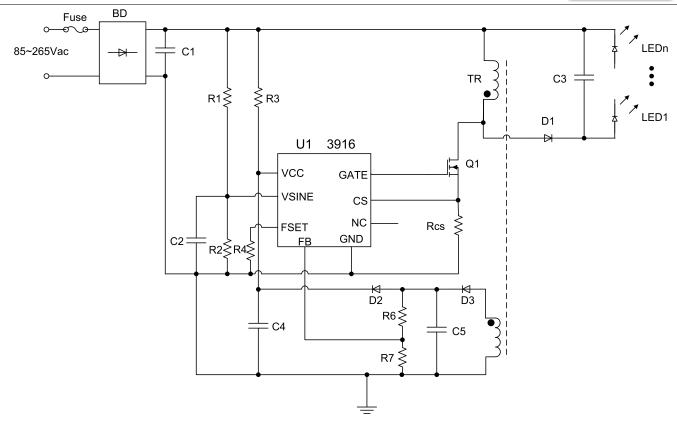

Figure 2 Typical Operating non-Isolated Circuit

Copyright © 2013 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any published information and before placing orders for products. Integrated Silicon Solution, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless Integrated Silicon Solution, Inc. receives written assurance to its satisfaction, that:

- a.) the risk of injury or damage has been minimized;

- b.) the user assume all such risks; and

- c.) potential liability of Integrated Silicon Solution, Inc is adequately protected under the circumstances

# Pin Configurations

| Package | Top View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|

| MSOP-8  | VSINE = 1 • VSINE = 2 · VSINE | 8 — VCC<br>7 — GATE<br>6 — CS<br>5 — FB |  |

#### **Pin Descriptions**

| Pin | Name  | Function                                                               |  |

|-----|-------|------------------------------------------------------------------------|--|

| 1   | VSINE | Line voltage sense input required for PFC.                             |  |

| 2   | NC    | No connect. Must leave floating in the application.                    |  |

| 3   | FSET  | Connect a resistor from this pin to GND to set the operating frequency |  |

| 4   | GND   | Ground. Common to all internal circuitry.                              |  |

| 5   | FB    | Auxiliary winding voltage sensing pin for OVP.                         |  |

| 6   | CS    | Primary winding peak current detection input.                          |  |

| 7   | GATE  | Power NMOS gate driving output.                                        |  |

| 8   | VCC   | Internal circuit power supply input.                                   |  |

### **Ordering Information**

| Order Part No.      | Package           | QTY/Reel |

|---------------------|-------------------|----------|

| IS31LT3916-GRLS2-TR | MSOP-8, Lead-free | 2500     |

### **Absolute Maximum Ratings**

| Parameter                                                                  | Value           |

|----------------------------------------------------------------------------|-----------------|

| VCC to GND                                                                 | -0.3V to 24V    |

| VSINE, NC, FSET, CS, FB                                                    | -0.3V to 5.5V   |

| VCC Max. Input Current(note) 10mA                                          |                 |

| Operating Temperature Ranges: -45°C to +10                                 |                 |

| Junction Temperature Range 150°C                                           |                 |

| Storage Temperature Range                                                  | -65°C to +150°C |

| Package Thermal Resistance junction to ambient (θ <sub>JA</sub> ) 210 °C/W |                 |

| ESD Human Model                                                            | 2000V           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

$(\underline{Unless\ otherwise\ specified,\ VCC=16V,\ FB=0V,\ VSINE=2.5V,\ RSET=300K\Omega,\ and\ T_{amb}=25\ ^{o}C)}$

| Symbol              | Parameter                                      | Conditions                                                    | spec  |      |       | Unit  |

|---------------------|------------------------------------------------|---------------------------------------------------------------|-------|------|-------|-------|

| Syllibol            | r arameter                                     |                                                               | Min   | Тур  | Max   | Oilit |

| VCC                 | VCC operation range                            |                                                               | 9     |      | 22    | V     |

| Vth_s               | VCC start voltage threshold                    | VCC rising                                                    | 14.5  | 16   | 17.5  | ٧     |

| Vth_d               | VCC under voltage threshold                    | VCC falling                                                   | 7     | 8    | 9     | V     |

| $V_{GATEclp}$       | GATE output voltage clamp value                | VCC =22V                                                      | 15    | 17.5 | 19    | ٧     |

| Icc                 | Quiescent Supply Current                       | Not switching                                                 |       | 800  |       | uA    |

| Ist                 | Startup current                                | VCC < Vth_s                                                   |       | 60   | 80    | uA    |

| Vcs                 | Primary peak current control threshold voltage |                                                               | 0.493 | 0.5  | 0.507 | V     |

| $T_{blank}$         | Blanking time                                  |                                                               |       | 500  | 800   | ns    |

| Tr                  | Rise time                                      | VCC=16V,CL=1nF,V <sub>GA</sub><br><sub>TE</sub> from 0V to 7V |       | 100  | 120   | ns    |

| Tf                  | Fall time                                      | VCC=16V,CL=1nF                                                |       | 50   | 80    | ns    |

| $V_{\text{ovp\_H}}$ | OVP rising voltage threshold of FB             |                                                               | 1.2   | 1.25 | 1.3   | ٧     |

| V <sub>ovp_L</sub>  | OVP falling voltage threshold of FB            |                                                               | 0.95  | 1.0  | 1.05  | V     |

| f                   | Operating frequency                            | RSET = 300k                                                   | 49    | 50   | 51    | kHz   |

| T <sub>OCP</sub>    | CS over current protection delay               | F = 50kHz                                                     | 500   | 600  | 750   | us    |

| Vocp-th             | CS over current protection threshold           | F = 50kHz                                                     | 0.65  | 0.7  | 0.75  | V     |

#### **Typical Performance Characteristics**

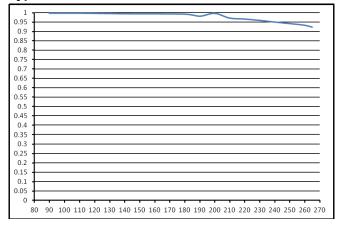

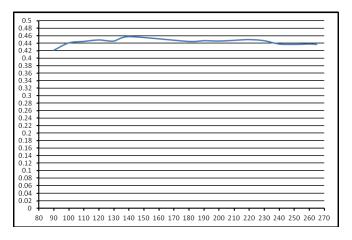

Figure 3 Vin VS PF (Output: Vout=40V lout=0.45A)

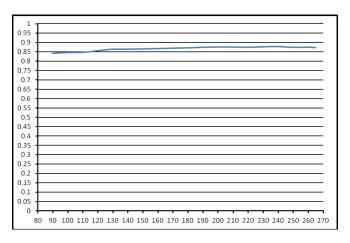

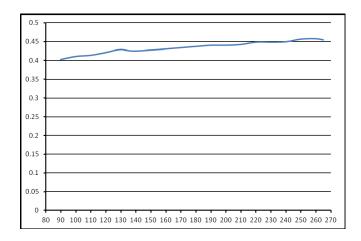

Figure 4 Vin VS Efficiency (Output:Vout=40V lout=0.45A)

Figure 5 Vin VS lout (Output: Vout=40V lout=0.45A with line compensation circuit)

Figure 6 Vin VS lout (Output: Vout=40V lout=0.45A without line compensation circuit))

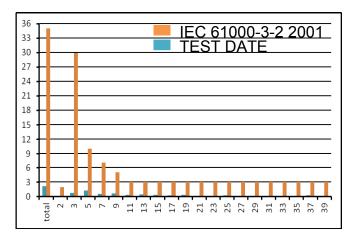

Figure 7 THD of Vin=110V (Output: Vout=40V lout=0.45A)

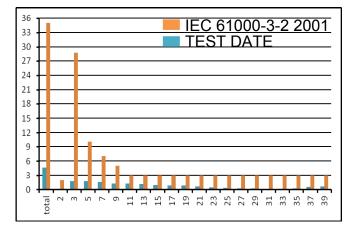

Figure 8 THD of Vin=220V (Output: Vout=40V lout=0.45A)

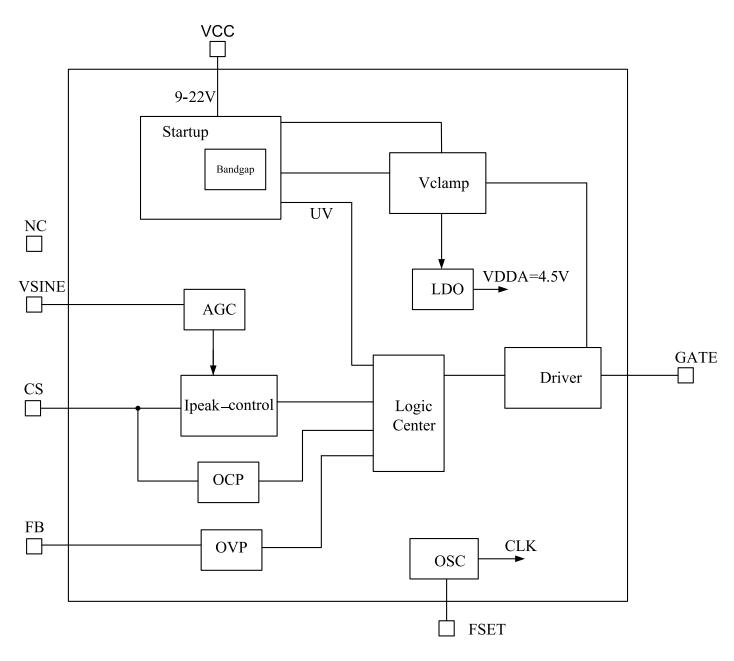

#### **Block Diagram**

Figure 9 Block Diagram

#### **Application Information**

#### Startup voltage

After power is applied to the circuit, R3 provides a trickle current to allow C4 to begin charging. The IC starts working when the voltage of C4 reaches the start threshold for the IC of 16.5V. The value of R3 & C4 can be determined by the input voltage. Choosing a larger value of R3 increases the startup time, but reduces the power losses after the circuit is running. A low ESR capacitor of 10uF, 25V is recommended for C4.

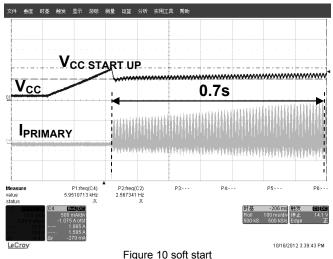

#### Soft start control

When the IC is initially powered up, the internal AGC output is at the minimum value, so the peak CS threshold is initially much less than 0.5V. The AGC steps up cycle by cycle until the CS threshold at the peak of the input sine wave is equal to 0.5V. In this manner, it will take several cycles of the AC waveform for the final value of current to be attained, as shown in Figure 9.

#### **GATE** output voltage clamp

IS31LT3916 has the voltage clamp for GATE output. When the voltage of VCC is smaller than the V<sub>GATECID</sub> threshold, the output high voltage of GATE output is about VCC. When the voltage of VCC is greater than V<sub>GATEclp</sub> threshold, the output high voltage of GATE is limited to the V<sub>GATEclp</sub> threshold.

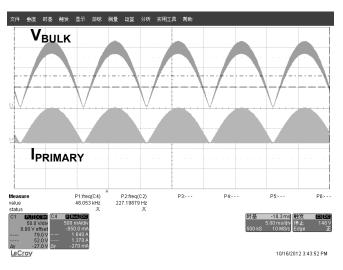

#### **VSINE** detection network and active PFC

The voltage of VSINE pin is used to control the waveform of input current make it follow the input voltage waveform, V<sub>BULK</sub>, to achieve high PF and low THD performance, as shown in figure 11.

Figure 11 Active PFC

VSINE is used to detect the input voltage which controls the peak current waveform in the primary inductor. An integrated AGC ensures that the peak current of the inductor remains constant with changing input voltage. This allows the IS31LT3916 to actively correct the power factor while maintaining a constant power output during operation. The internal AGC is designed for an input range of 0.8V to 2.5V at the VSINE pin, meaning that the AGC gain achieves a minimum value when the voltage at VSINE is 2.5V, however, there is no internal voltage clamp preventing the VSINE voltage from exceeding 2.5V. If the peak input voltage at VSINE exceeds 2.5V, the CS threshold can no longer be maintained at 0.5V, causing the line regulation to suffer. Thus, the resistor network connected to VSINE should be computed such that the worst case peak input voltage condition corresponds to ~2.4V. Thus, for 265VAC, the peak voltage is 374.7V. At 374.7V input, the output of the network should be 2.4V, thus values of R1=1.86M and R2 = 12k are appropriate. High tolerance Resistance value of 1% should be used. A small capacitor, C2, is used to filter high frequency noise that may couple to the VSINE pin.

# ISSI

#### **Working Frequency**

The working frequency is set by connecting a resistor between the FSET pin and ground. The relationship between the frequency and resistance is:

$$f = \frac{15 \times 10^9}{R_{EXT}}$$

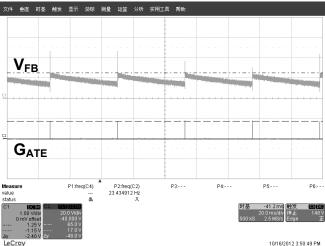

#### Output open circuit protection

Open circuit protection is realized by connecting a resistor network from the auxiliary winding to the FB pin. By sensing the voltage of the auxiliary winding, which is proportional to the output voltage, the IS31LT3916 detects when there is an open circuit condition on the secondary and consequently stop the switching action. The threshold voltage for the FB pin is 1.25V.

Figure 12 Output open circuit protect

#### **Output short circuit protection**

If the output of the circuit is suddenly shorted, the voltage of the secondary winding is quickly reduced. This in-turn reduces the reflected voltage in the auxiliary winding, so VCC of the device drops rapidly. If the VCC voltage drops below the UVLO, the device will stop switching, thus indirectly achieving output short circuit protection.

Figure 13 Output short circuit protect

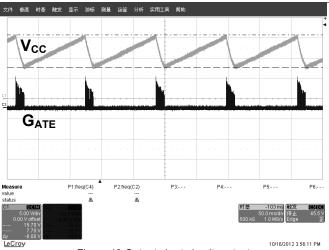

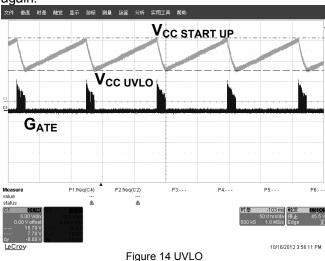

#### **UVLO** protection

After triggering the device UVLO, the device will stop operating until the VCC voltage raises above the startup threshold, at which point the device will start again.

Line regulation compensation design

The output power of IS31LT3916 varies slightly with input voltage due to the small delay associated with the current sense control loop. At high input voltages, the slope of the input current is quite steep, and, thus, will overshoot the target value by more than at low input voltage conditions. Therefore, under wide input voltage conditions, and without additional compensation, the output power varies over the full input voltage range, 85VAC to 265VAC, by about +/-5%. To further improve the line regulation, a simple compensation circuit may be added, as in Figures 16 & 17, components R7, R11, R15, R19, R16 and C8.

#### Transformer design

The transformer design is beyond the scope of the datasheet. Refer to the document entitled "3916 calculator" to design the transformer.

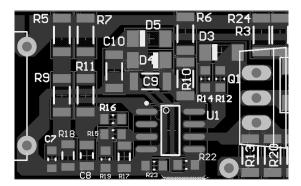

#### PCB design considerations

- (1) As Figure 15 shows, Components such as R17,R13,R20,R21,R22, R23, R18, C7, C9etc. Which are connected to the IC should be mounted as close to the IC as possible.

- (2) Bypass capacitors should always be mounted as close to the IC as possible.

- (3) Switching signal traces should be kept as short as possible and not be routed parallel to one another so as to prevent coupling.

- (4) It is best to keep Power Ground and Signal Ground separate, and make the traces of Power Ground as short as possible.

Figure 15 typical PCB layer out

Typical Application Circuit (Full input voltage range, output: 40V, 0.45A)

Figure 16 Typical Isolation Application Circuit

Figure 17 Typical Non-isolation Application Circuit

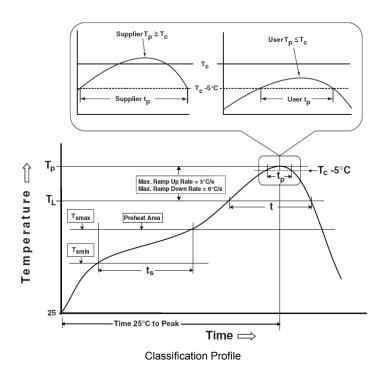

#### **Classification Reflow Profiles**

| Profile Feature                                                                           | Pb-Free Assembly                 |  |  |

|-------------------------------------------------------------------------------------------|----------------------------------|--|--|

| Preheat & Soak Temperature min (Tsmin) Temperature max (Tsmax) Time (Tsmin to Tsmax) (ts) | 150°C<br>200°C<br>60-120 seconds |  |  |

| Average ramp-up rate (Tsmax to Tp)                                                        | 3°C/second max.                  |  |  |

| Liquidous temperature (TL) Time at liquidous (tL)                                         | 217°C<br>60-150 seconds          |  |  |

| Peak package body temperature (Tp)*                                                       | Max 260°C                        |  |  |

| Time (tp)** within 5°C of the specified classification temperature (Tc)                   | Max 30 seconds                   |  |  |

| Average ramp-down rate (Tp to Tsmax)                                                      | 6°C/second max.                  |  |  |

| Time 25°C to peak temperature                                                             | 8 minutes max.                   |  |  |

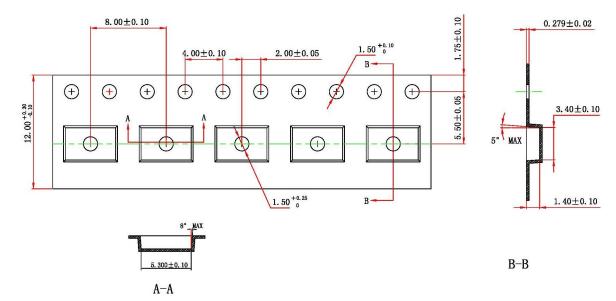

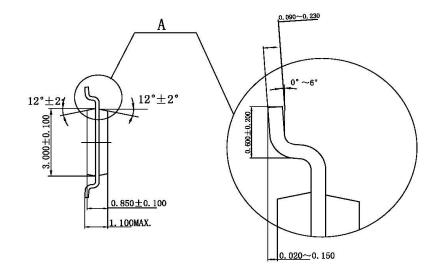

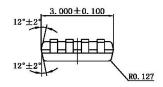

### **Tape and Reel Information**

#### NOTES:

NOTES.

1.CARRIER TAPE COLOR: BLACK

2.COVER TAPE WIDTH: 9.30±0.10

3.COVER TAPE COLOR: TRANSPARENT

4. ANTISTATIC COATED 10<sup>5-</sup> 10<sup>1</sup>OHMS/SQ.

5.10 SPROCKET HOLE PITCH CUMULATIVE TOLERANCE ±0.20MAX.

6.CAMBER NOT TO EXCEED 1 MM IN 100 MM

7.MOLD# MSOP8/10

8.ALL DIMS IN mm.

9.THE DERECTION OF VIEW:

Integrated Silicon Solution, Inc. – www.issi.com Rev. 0A, 1/25/2013

# ISSI

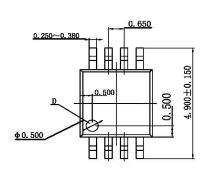

### Package Information

THE REQUEST OF TECHNOLOGY

1. DETAIL "D" ROUND SURFACE SHOULD BE POLISHED FINISH;

- 2. COPLANARITY: 0.05;

- 3. ALL UNITS ARE IN MILLIMETER;

- 4. THE DERECTION OF VIEW: